Comme tant d’autres, la firme californienne Cerebras Systems regroupe des architectes informaticiens, des informaticiens et des chercheurs pionniers dans le domaine de l’apprentissage profond. Elle se différencie toutefois par les efforts qu’elle déploie pour réaliser une nouvelle classe de systèmes informatiques qui accélèrent l’intelligence artificielle par des ordres de grandeur dépassant l’état actuel de la technique.

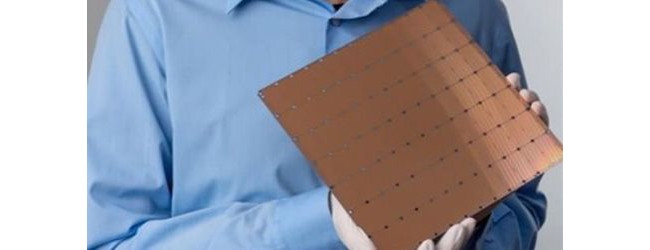

Tout récemment, elle a d’ailleurs fait la Une de la presse spécialisée en annonçant avoir conçu la plus grande puce informatique au monde pour les tâches d’intelligence artificielle, dont celle pilotage de systèmes d’intelligence artificielle complexes comme les voitures sans conducteur ou les logiciels de surveillance. Cette popularité est cependant tout à fait justifiée quand on connaît les propriétés de cette puce hors normes.

Dénommée WSE (pour Wafer Scale Engine) et présentée en première mondiale lors de la récente conférence Hot Chips (18 au 20 août à l’Université Stanford), cette puce de 46,225 mm2 ne contient rien de moins que 1,2 billion de transistors et 400 000 noyaux optimisés pour l’intelligence artificielle. Chaque noyau est flexible, programmable et optimisé pour les calculs qui sous-tendent la plupart des réseaux neuronaux. La programmabilité garantit que les cœurs peuvent exécuter tous les algorithmes dans le domaine de l’apprentissage machine, un domaine en constante évolution. En fait, elle est conçue pour résoudre des problèmes d’apprentissage automatique en intelligence artificielle et sa commercialisation pourrait donner lieu à des modifications jusqu’ici insoupçonnées en matière de conception des réseaux d’apprentissage en profondeur.

Interrogé par ZNet, Pierre Lamond, associé principal chez Eclipse Ventures de Palo Alto, en Californie, affirme sans ambages qu’« Il faudra au moins deux à trois ans à la concurrence pour proposer un produit similaire ».

«La loi de Moore [qui postule que le nombre de transistors des microprocesseurs (et non plus de simples circuits intégrés moins complexes) sur une puce de silicium double tous les deux ans] n’est pas mauvaise, mais elle ralentit, fait remarquer Pierre Lamond, évoquant les difficultés qui empêchent de progresser de plus en plus vers des fonctionnalités de plus en plus sophistiquées. La grande question pendant longtemps, et c’est là que Cerebras a innové, est : OK, sommes-nous limités à une puce de deux par trois, trois par cinq centimètres, ou allons-nous à quelque chose de beaucoup plus gros ? Il est devenu évident qu’à moins de prendre le risque de fabriquer un très gros morceau et de trouver le moyen de le faire fonctionner comme un système, il n’y aura aucun progrès.»

Dotée d’une surface de silicium plus grande unité de traitement graphique, le WSE fournit plus de cœurs de calcul, une mémoire étroitement couplée pour un accès efficace aux données et un tissu de communication à large bande passante pour que des groupes de cœurs puissent travailler ensemble.

Les 400 000 cœurs du WSE sont connectés par le biais d’un tissu de communication Swarm dans un maillage 2D avec 100 Pb/s de bande passante. Ce tissu de communication massive sur puce offre une capacité de bande passante inédite et une faible latence à une fraction de la consommation électrique des techniques traditionnelles utilisées pour regrouper les unités de traitement graphique. Tout cela grâce à 18 giga-octets de mémoire sur puce, tous accessibles en un seul cycle d’horloge, et une bande passante mémoire de 9 Pb/s. Ce qui se traduit par 3 000 fois plus de capacité et 10 000 fois plus de bande passante que le principal concurrent du WSE. En d’autres mots, la méga puce de silicium mise au point par Cerebras est rien de moins cinquante-sept fois plus grande que la plus grande unité de traitement graphique de Nvidia, son plus proche concurrent.

« En plus des innovations de base en matière de fabrication, le matériel présente d’autres innovations, ajoute Pierre Lamond. Cerebras a mis au point un moyen de détecter, dans le matériel, les éléments de valeur zéro dans un réseau de neurones afin d’éviter de les calculer. Ce [ce qui constitue] un développement très astucieux de découvrir les zéros dans le matériel, de sorte que vous n’utilisez pas de logiciel pour le faire. Cela économise des cycles. »

https://www.cerebras.net/

Print this page